AI Agent重构芯片设计:EDA三巨头的"硅基智能体"革命与UltraLAB算力底座配置指南

时间:2026-03-20 11:22:32

来源:UltraLAB图形工作站方案网站

人气:50

作者:管理员

——当ChipStack遇见AgentEngineer,芯片设计从"人驱动工具"进化为"AI自主设计"

2026年3月,Cadence Converge大会、CES 2026、DesignCon 2026相继落幕,一个清晰的信号释放:传统EDA工具正在进化为AI驱动的系统级工程平台。

Cadence的ChipStack AI Super Agent实现验证效率10倍提升;Synopsys的AgentEngineer技术将RTL设计周期从6个月压缩至数周;Siemens联合NVIDIA构建工业AI操作系统...这场变革的背后,是芯片设计复杂度指数级增长与资深工程师短缺的双重困境。

当70%的研发时间耗费在电路描述与验证上,AI Agent不再是"辅助工具",而是成为"虚拟工程师"。本文将深度拆解EDA三巨头的AI技术路线、核心算法,并提供支撑这些智能工作流的UltraLAB硬件配置方案。

一、行业痛点:为什么传统EDA流程亟需AI革命?

在3nm/2nm工艺节点,芯片设计面临前所未有的挑战:

-

设计空间爆炸:数十亿晶体管、千级时钟域、复杂多物理场耦合

-

验证成本黑洞:验证占研发时间的70%,且呈指数级增长

-

人才严重短缺:资深EDA工程师培养周期长达5-10年

-

工艺微缩红利衰减:单纯依赖制程提升已无法满足性能需求

行业共识:必须从"工程师手动迭代"转向"AI自主设计优化"。

二、EDA三巨头AI布局深度解析

2.1 Cadence:ChipStack AI Super Agent——首个代理式AI工作流

核心产品:ChipStack™ AI Super Agent(2026年3月发布)

技术架构:

-

多智能体协作(Multi-Agent Orchestration):协调多个"虚拟工程师"并行工作

-

云端+本地混合部署:支持NVIDIA Nemotron开源模型(本地)+ OpenAI GPT(云端)

-

全流程自动化:RTL设计 → Lint检查 → 测试平台生成 → 仿真验证 → 自动修复

关键技术突破:

| 技术模块 | 核心算法 | 效率提升 |

|---|---|---|

| RTL生成代理 | 大语言模型(LLM)+ 形式化规范解析 | 代码生成速度提升10倍 |

| 验证代理 | 强化学习驱动的测试向量生成 | 验证工作量缩减10倍 |

| 调试代理 | 图神经网络(GNN)错误定位 | 调试时间缩短4倍 |

| 收敛优化 | 贝叶斯优化+遗传算法 | 自动收敛至时序/功耗目标 |

配套软件栈:

bash

# Cadence AI核心组件 ChipStack AI Super Agent # 代理式AI工作流平台 JasperGold # 形式化验证(集成AI辅助断言生成) Genus / Innovus # 逻辑综合与物理实现(AI驱动布局布线) Tempus / Voltus # 时序/功耗签核(AI预测极端工况) Xcelium # 仿真平台(AI加速testbench生成)

客户实证:

-

Altera:验证工作量缩减10倍

-

Tenstorrent:关键模块验证时间缩短4倍

-

NVIDIA:AI成为设计新一代芯片的必备工具

2.2 Synopsys:AgentEngineer——L4级自主设计工作流

核心产品:AgentEngineer™技术驱动的L4编排式多智能体工作流

技术架构:

-

从硅到系统(Silicon to System):整合Ansys多物理场能力

-

L4级自主性:自然语言→RTL→验证→收敛的全自主闭环

-

多物理场融合(Multiphysics Fusion™):电磁-热-机械效应联合仿真

关键技术突破:

| 技术模块 | 核心算法 | 应用场景 |

|---|---|---|

| RTL生成 | 生成式AI(Transformer架构) | 从自然语言规范生成可综合RTL |

| 多物理场签核 | 物理信息神经网络(PINNs) | 电压降+热分析联合签核 |

| 电子数字孪生(eDT) | 高保真系统级仿真 | 硬件可用前完成90%软件验证 |

| 设计空间探索(DSE) | 强化学习+代理模型 | 自动寻找PPA最优解 |

配套软件栈:

bash

# Synopsys AI核心组件 Synopsys.ai # AI驱动EDA全家桶 AgentEngineer # L4级智能体工作流 DSO.ai # 设计空间优化(强化学习) VCS AI # AI加速仿真收敛 PrimeSim AI # AI加速电路仿真(替代传统SPICE) Ansys RedHawk / Totem # 多物理场签核(电磁-热-可靠性)

客户实证:

-

前端设计周期:从4-6个月缩短至数周(生产力提升2-5倍)

-

汽车电子:eDT平台实现硬件可用前90%软件验证

2.3 Siemens EDA:Questa One Agentic Toolkit——工业AI操作系统

核心产品:Questa One Agentic Toolkit(2026年2月发布)

技术架构:

-

NVIDIA深度集成:集成NVIDIA NIM微服务 + Nemotron开源模型

-

领域限定代理(Domain-Specific Agents):5大专业智能体协同

-

工业级可靠性:符合ISO 26262等车规标准

五大智能体功能:

| 智能体 | 核心能力 | 技术实现 |

|---|---|---|

| RTL代码代理 | 自然语言→可综合RTL + 编码规范检查 | LLM + RAG(EDA知识库) |

| Lint代理 | 自动配置Lint规则 + 违规修复建议 | 静态分析 + 模式匹配 |

| CDC代理 | 时钟域交叉验证自动配置与执行 | 形式化验证 + ML加速 |

| 验证规划代理 | 从设计规范自动生成验证计划 | NLP + 覆盖率分析 |

| 调试代理 | 波形-断言-日志智能关联分析 | 时序图神经网络(T-GNN) |

配套软件栈:

bash

# Siemens AI核心组件 Questa One Agentic Toolkit # 智能验证平台 PADS / Xpedition # PCB设计(集成AI布局) Calibre # 物理验证(AI辅助DRC修复) AFS / Eldo # 模拟电路仿真(AI加速) Tessent # 测试与良率分析(AI缺陷预测)

客户实证:

-

联发科:通常需要数天的任务数小时内完成,掌握需数周培训的工作流数小时内上手

三、AI-EDA关键技术深度拆解

3.1 代理式AI(Agentic AI)架构

三大巨头共同采用的技术范式:

plain

用户意图(自然语言/规范)

↓

[规划Agent] → 任务分解(RTL设计?验证?调试?)

↓

[专业Agent集群] 并行执行

├─ RTL Agent:生成代码

├─ Lint Agent:静态检查

├─ Sim Agent:仿真验证

└─ Debug Agent:错误修复

↓

[协调器] → 结果融合 → 反馈优化

↓

输出:签核通过的RTL + 验证报告

核心算法:

-

ReAct(Reasoning + Acting):代理先推理再执行,支持多步规划

-

RAG(Retrieval-Augmented Generation):外挂EDA知识库,避免LLM幻觉

-

多智能体强化学习(MARL):多个代理协作优化全局PPA目标

3.2 生成式AI在EDA中的应用

| 应用场景 | 输入 | 输出 | 底层模型 |

|---|---|---|---|

| RTL生成 | "设计一个AXI4总线仲裁器" | SystemVerilog代码 | CodeLlama-70B / GPT-4 |

| Testbench生成 | RTL代码 | UVM测试平台 | 微调Seq2Seq模型 |

| 断言生成 | 设计规范 | SVA断言 | Transformer + 形式化验证 |

| 文档生成 | RTL代码 | 设计文档/时序图 | 多模态LLM |

| 布局布线 | 网表 + 约束 | GDS版图 | 图神经网络(GNN)+ 强化学习 |

3.3 多物理场融合计算

Synopsys Multiphysics Fusion™核心技术:

-

电磁-热耦合:提取功耗分布 → 热仿真 → 温度反馈影响电导率

-

热-机械耦合:温度梯度 → 热应力分析 → 翘曲/可靠性预测

-

算法:物理信息神经网络(PINNs)加速多物理场迭代

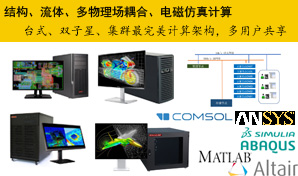

四、UltraLAB AI-EDA工作站配置方案

AI-EDA工作流对硬件提出独特需求:大显存(加载数十亿参数LLM)、高内存带宽(多物理场矩阵求解)、低延迟(实时交互设计)。

方案A:AI驱动前端设计工作站(适合RTL设计/验证工程师,预算25-40万)

定位:本地运行ChipStack/Questa One Agentic Toolkit,支持70B级LLM推理

| 组件 | 推荐配置 | 技术理由 |

|---|---|---|

| CPU | AMD Threadripper PRO 7995WX (96核192线程) | 多核并行Lint/CDC检查,高频加速编译 |

| GPU | NVIDIA RTX 6000 Ada 48GB ×2 (NVLink) | 96GB显存池化,支持70B模型(INT4)本地部署;双卡加速AI代码生成 |

| 内存 | 512GB DDR5-5600 ECC | 加载大型SoC设计(>10M实例)+ LLM上下文缓存 |

| 存储 | 4TB PCIe 5.0 NVMe (RAID 0) | 快速加载EDA工具与IP库 |

| 网络 | 双口25GbE | 连接企业Librarian/IP服务器 |

| 软件栈 | Cadence ChipStack + Synopsys.ai + Questa One | 三巨头AI平台并行验证 |

性能指标:

-

RTL代码生成速度:~1000 lines/s(对比传统手写50 lines/s)

-

本地LLM推理延迟:< 2秒(70B模型)

-

千万门级SoC仿真:支持并行256个testbench

方案B:多物理场签核服务器(适合Sign-off工程师,预算45-70万)

定位:支撑Synopsys Multiphysics Fusion™、Ansys RedHawk电热联合仿真

| 组件 | 推荐配置 | 技术理由 |

|---|---|---|

| CPU | 2× Intel Xeon W9-3595X (128核256线程, 4.8GHz) | 高主频加速SPICE仿真,多核并行EM/IR分析 |

| GPU | NVIDIA H100 80GB ×2 (NVLink) | 80GB显存支撑十亿级单元网表;Tensor Core加速PINNs多物理场求解 |

| 内存 | 1TB DDR5-4800 ECC RDIMM | 支撑3DIC多芯片系统的完整网表(>50M单元) |

| 存储 | 8TB NVMe RAID 0 + 20TB SATA | 高速存储GDS版图与仿真结果(单芯片GDS可达TB级) |

| 专业软件 | Ansys RedHawk-SC + Synopsys PrimeSim + Voltus | 多物理场签核全家桶 |

性能指标:

-

电源完整性分析:支持十亿级节点,速度提升10倍(对比传统流程)

-

电热联合仿真:迭代收敛速度提升5倍

-

3DIC热分析:支持12层堆叠芯片全系统仿真

方案C:企业级AI-EDA私有云平台(适合芯片设计企业/研究院,预算150万+)

定位:构建企业私有"硅基智能体"平台,支持多项目并行AI设计

架构设计:

-

AI训练节点:H100 80GB ×8,训练企业专属EDA大模型(基于内部IP库微调)

-

推理服务节点:RTX 6000 Ada ×8,部署ChipStack/AgentEngineer推理服务(API化)

-

仿真加速节点:Xeon W9-3595X + RTX 5000 Ada,运行VCS/Xcelium并行仿真

-

多物理场节点:双路EPYC + H100,运行Ansys多物理场签核

-

调度系统:UltraLAB PSS作业调度,智能分配"AI推理"与"传统仿真"资源

软件栈:

bash

# AI基础设施 NVIDIA AI Enterprise # 企业级AI套件(含NIM微服务) vLLM / TensorRT-LLM # LLM推理加速 LangChain / LlamaIndex # Agent编排框架 # EDA工具链 Cadence ChipStack Enterprise # 企业级代理式AI Synopsys DSO.ai + VCS AI # 设计空间优化与AI仿真 Siemens Questa One # 智能验证平台 # MLOps MLflow / Weights & Biases # 模型版本管理与实验追踪五、实施路径:从"辅助设计"到"自主设计"

阶段一:AI辅助(当前-2026)

-

部署AI代码补全(GitHub Copilot for EDA)

-

使用AI生成Testbench(减少30%验证工作量)

-

硬件配置:单卡RTX 4090/5090工作站即可

阶段二:AI协同(2026-2027)

-

引入ChipStack/Questa One Agentic Toolkit

-

建立企业私有LLM(微调基础模型)

-

硬件配置:双卡RTX 6000 Ada + 大内存服务器

阶段三:AI自主(2027+)

-

实现L4级自主设计工作流

-

AI驱动的设计空间探索(DSE)成为主流

-

硬件配置:H100集群 + 企业级AI基础设施

结语:掌握进化的工具,掌握未来入场券

正如黄仁勋所言:"生成式AI和加速计算点燃了新的工业革命,将数字孪生从被动模拟转变为物理世界的主动智能。"

当Cadence、Synopsys、Siemens纷纷将AI Agent作为核心战略,芯片设计工程师的角色正在从"手动操作工具"进化为"指挥AI智能体"。而支撑这一变革的,是强大的本地算力底座——没有RTX 6000 Ada的48GB显存,就无法本地部署70B级的ChipStack模型;没有H100的Tensor Core,就无法实时运行多物理场PINNs求解。

UltraLAB致力于为AI-EDA时代提供最可靠的算力基础设施。无论您是验证工程师、RTL设计师,还是企业IT架构师,我们都有经过验证的硬件方案。

选择UltraLAB,让AI Agent成为您的"硅基设计伙伴",在芯片设计的智能革命中抢占先机。

本文技术参数参考Cadence Converge 2026、Synopsys官方技术白皮书、Siemens CES 2026发布资料及NVIDIA AI Enterprise最佳实践。

立即联系UltraLAB技术顾问,获取针对您EDA工具链(Cadence/Synopsys/Siemens)的定制化AI加速硬件方案。

UltraLAB图形工作站供货商:

西安坤隆计算机科技有限公司

国内知名高端定制图形工作站厂家

业务电话:400-705-6800

咨询微信号:xasun001

上一篇:没有了